ZYNQ硬件调试-------day2

ZYNQ硬件调试-------day2

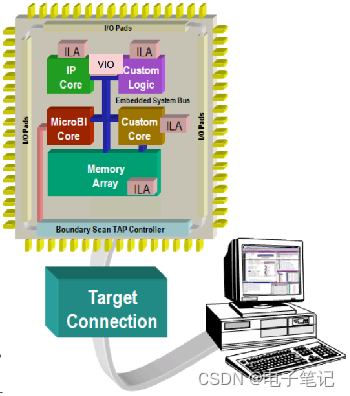

1.ILA(Integrated Logic Analyzer )

监控逻辑内部信号和端口信号;可以理解为输出。可单独使用

2.VIO(Virtual Input/Output )

实时监控和驱动逻辑内部信号和端口信号,可以理解为触发输入。不可单独使用

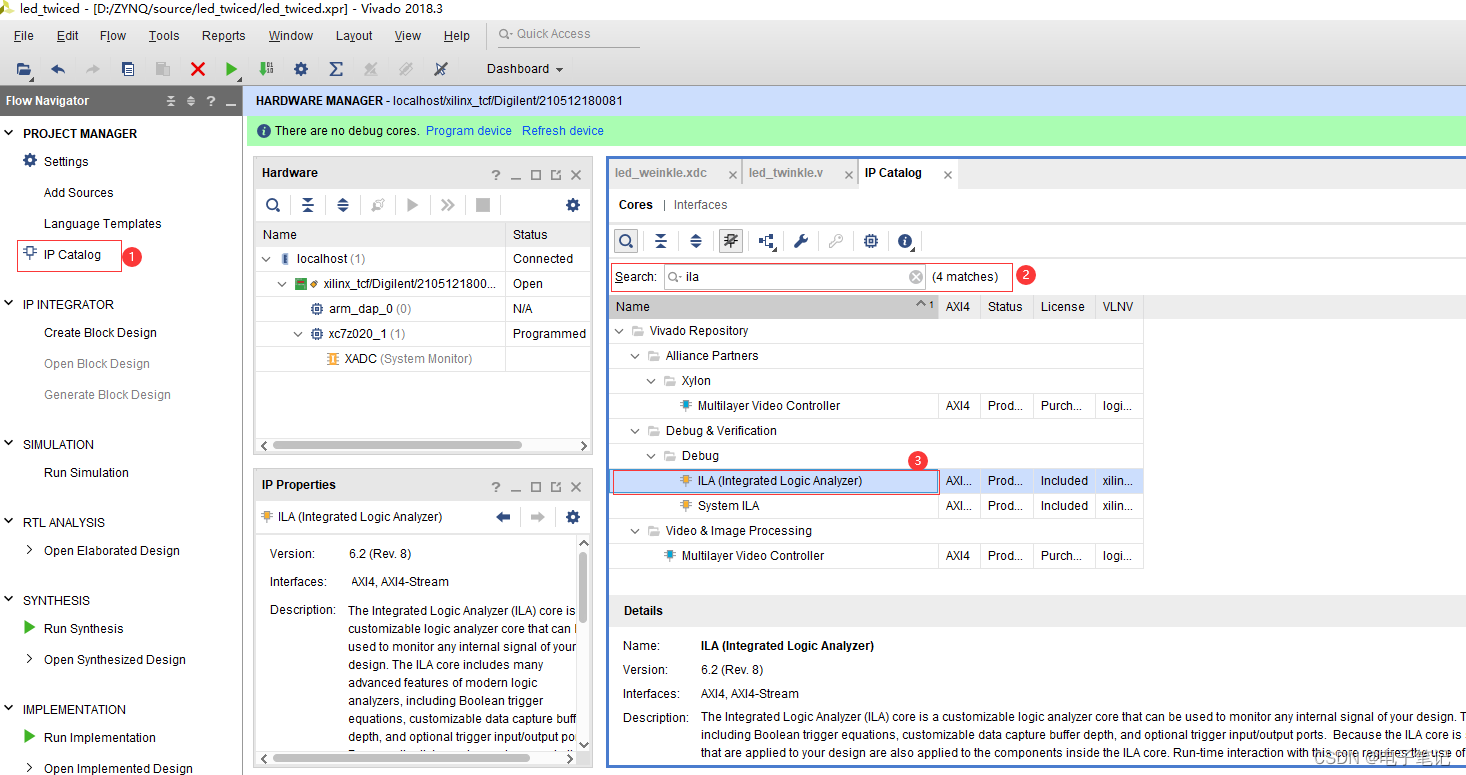

3.添加ILA核的几种方法

调用ILa进行仿真步骤:

双击3处弹出如下选项:

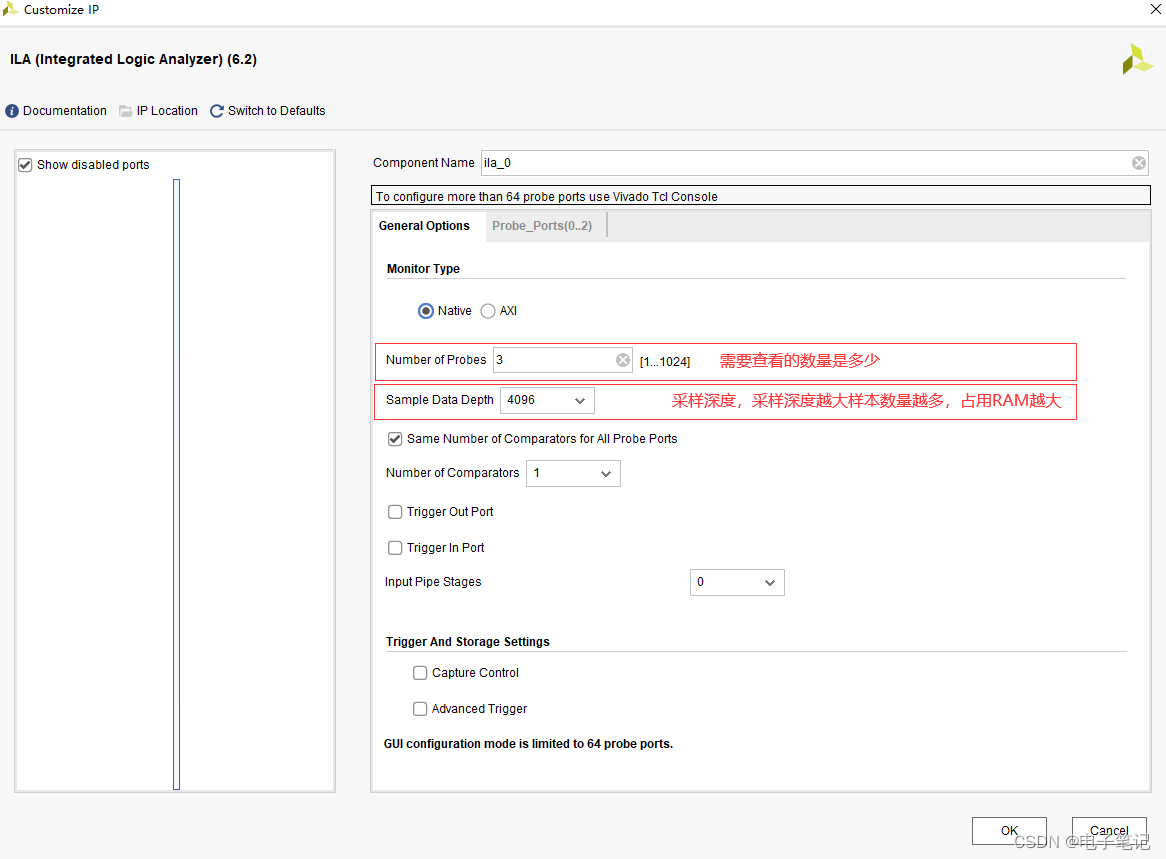

在“General Options”页面中, “Number of Probes” 一栏用于设置所需的探针数量,一般地,一个探针用于连接一个待测信号,例如,我们想要观察“sys_rst_n”、“led” 和“cnt” 这三个信号,则需要把“Numberof Probes” 设置为 3;

点击第二选项:

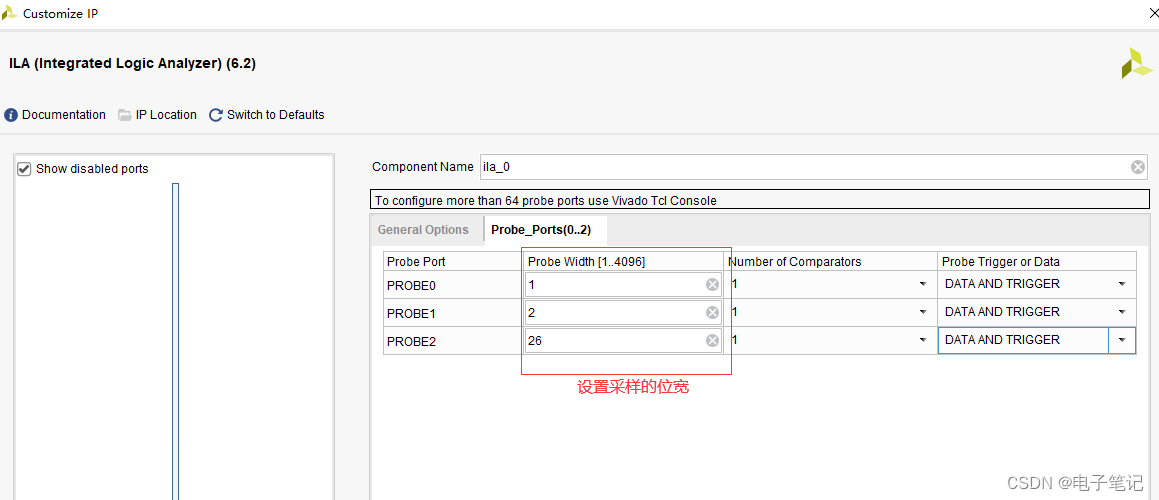

在“Probe_Ports(0…0)” 页面中,用于设置每个探针的参数,一般我们只需设置探针宽度“Probe Width[1…4096]”一栏即可,由于“sys_rst_n”、“led” 和“cnt” 这三个信号的位宽分别是 1 位、 2 位和 26 位,所以我们需要将其分别设置为 1、 2 和 26,然后点击“OK”按钮即可。

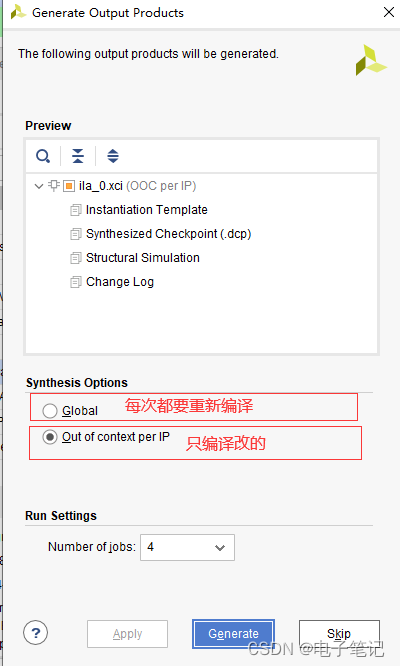

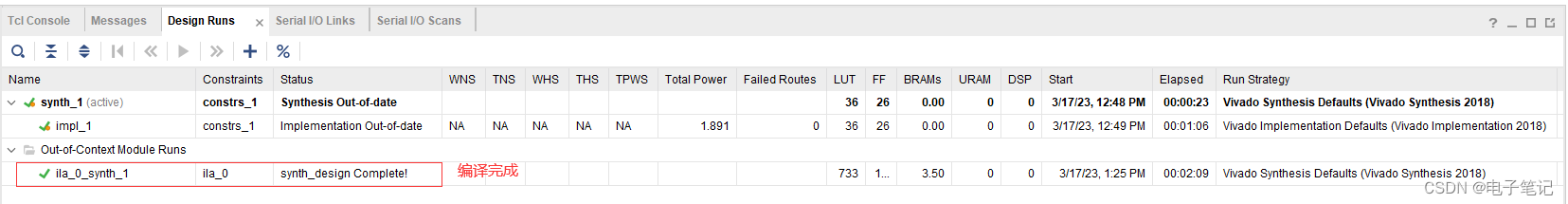

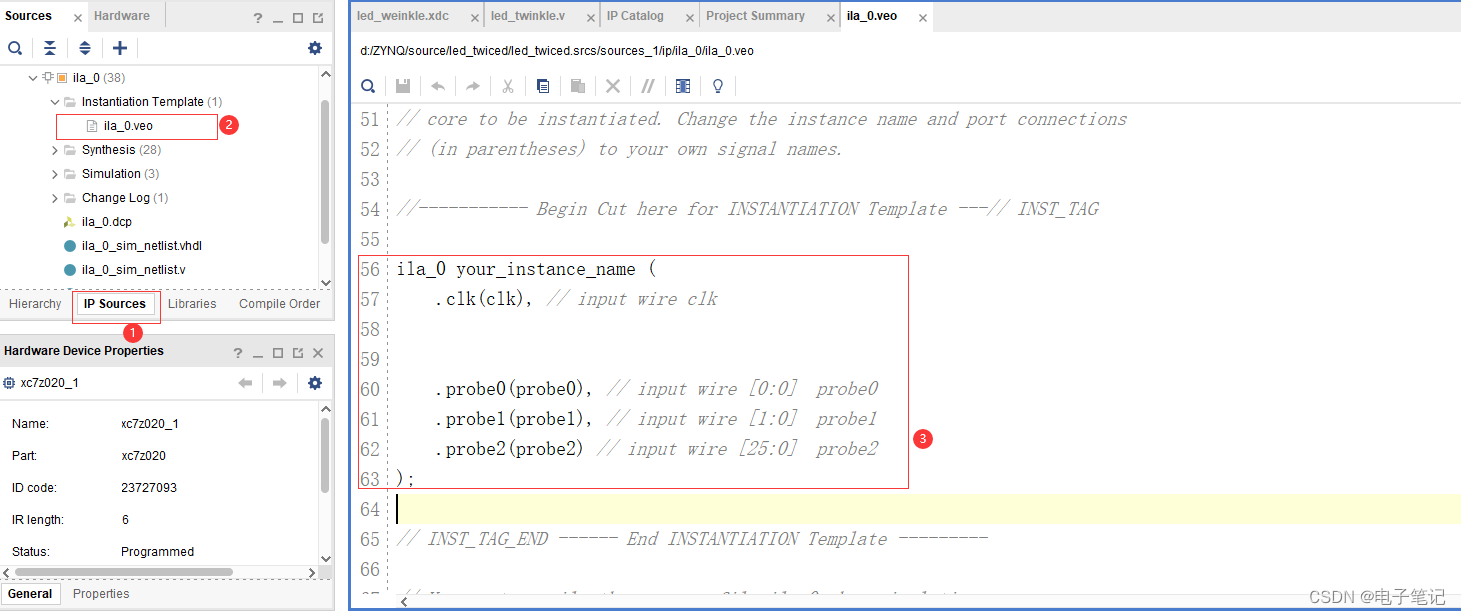

编译完成后如下图所示:

拷贝例程中的代码:

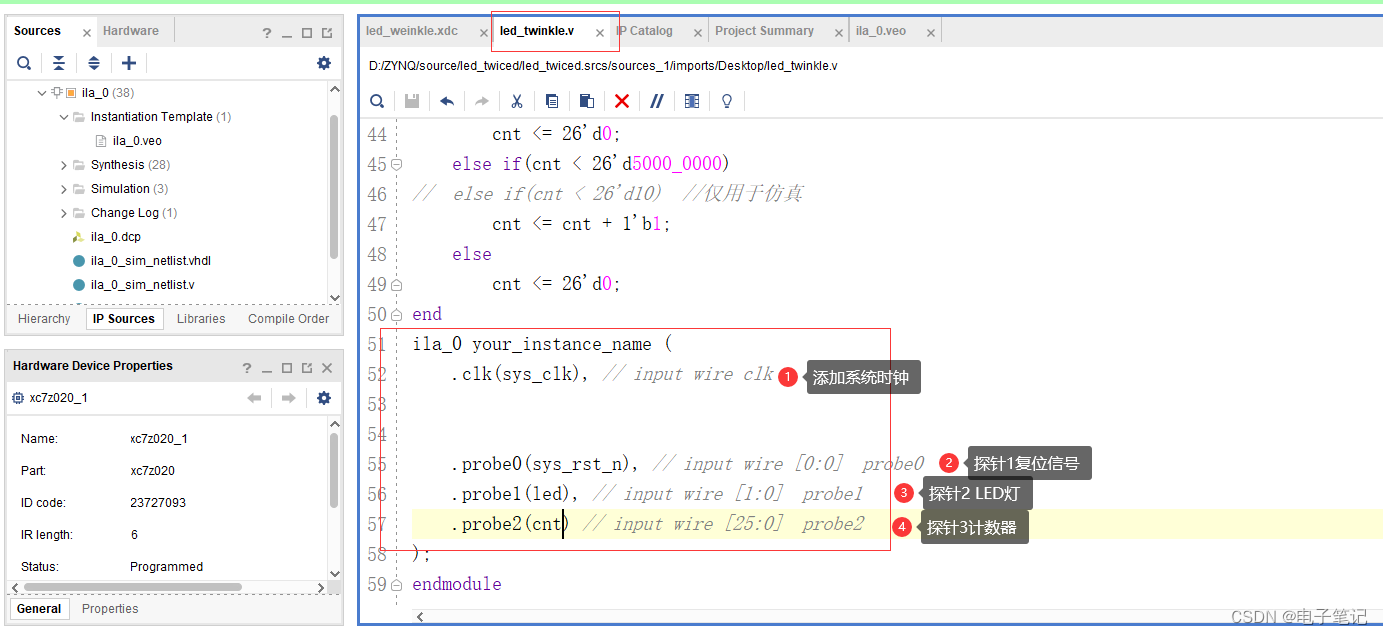

我们将 ILA 的时钟连接到了顶层时钟 sys_clk 信号上, probe0 探针连接到了 sys_rst_n, probe1 探针连接到了 led, probe2 探针连接到了 cnt。 代码修改完成后如下图所示:

保存源文件之后就可以直接综合并实现设计,最后生成比特流。

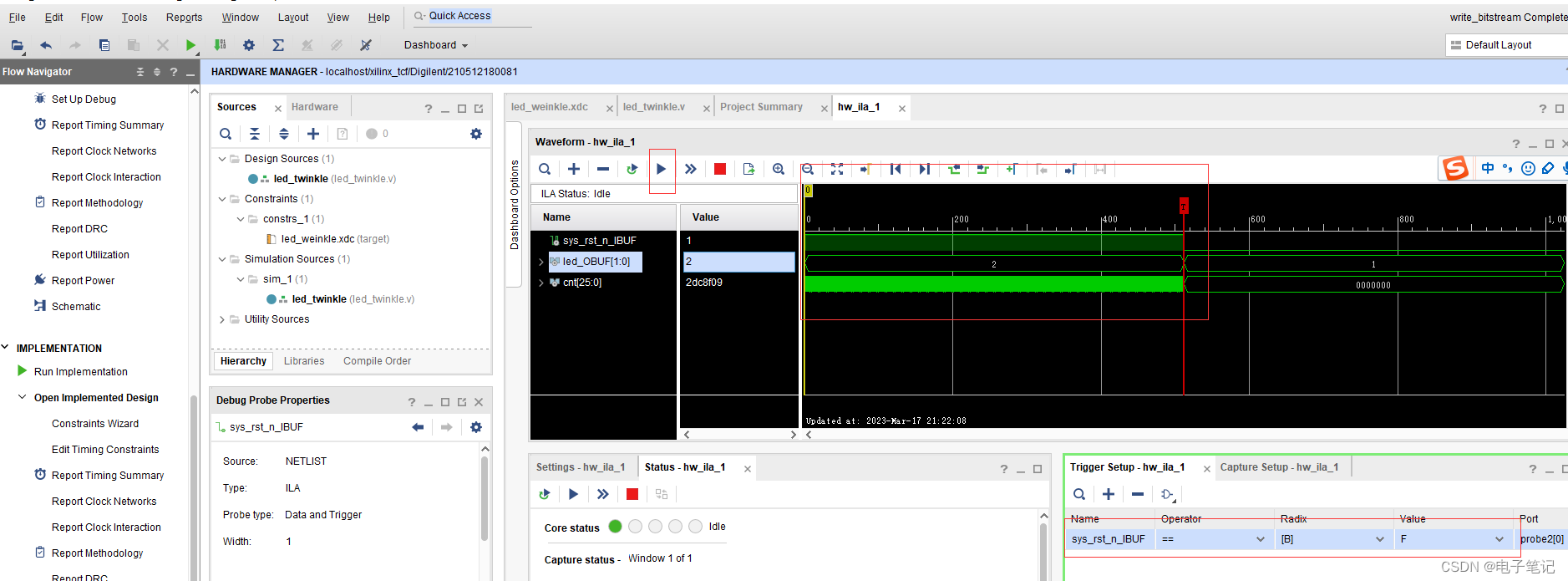

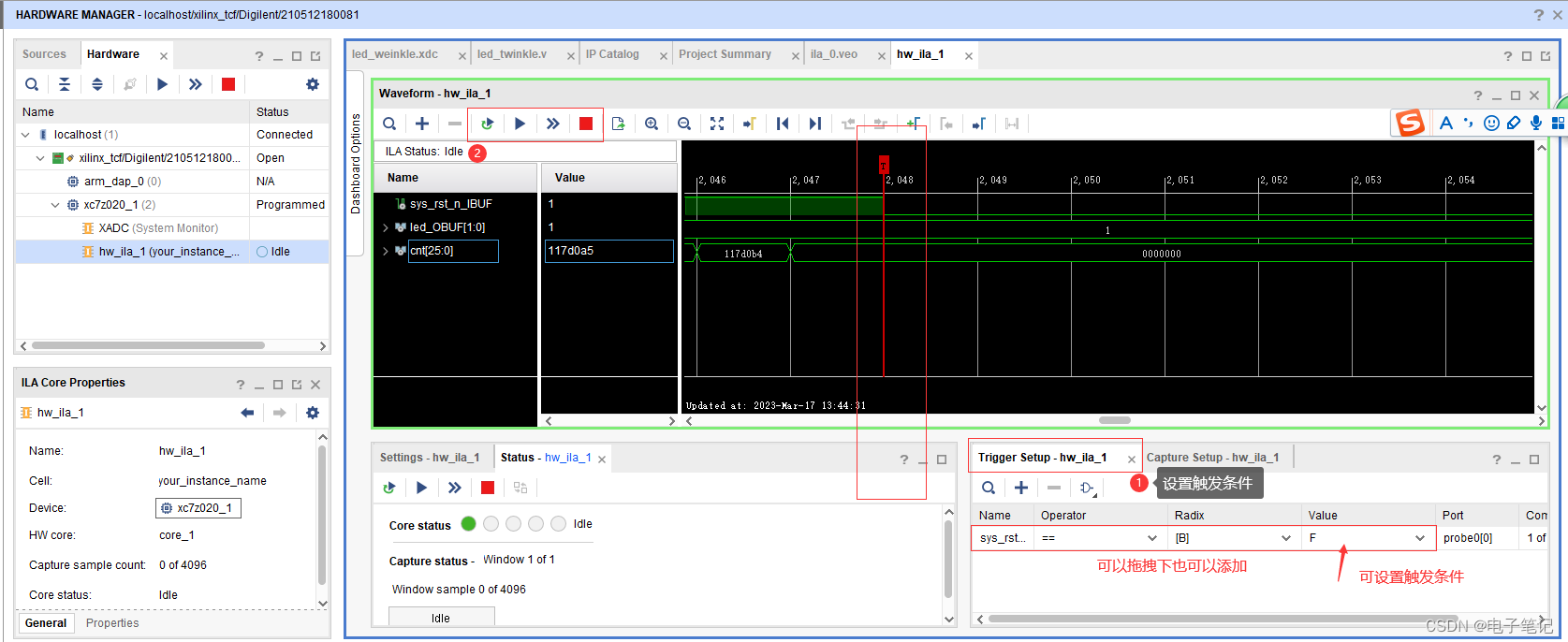

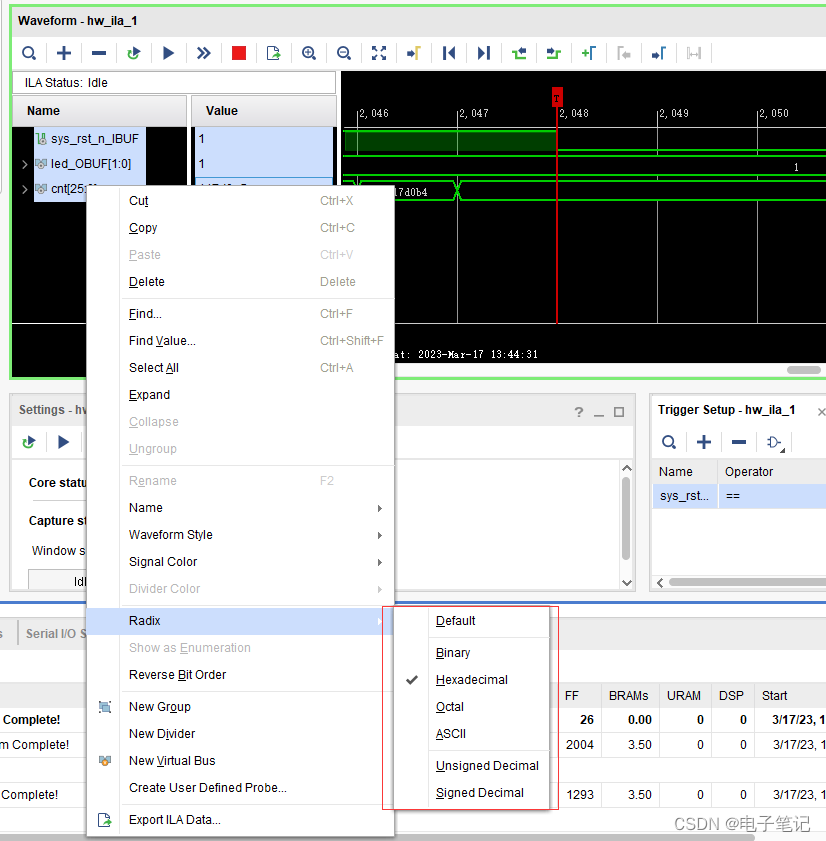

可设置选择的进制:

从左至右依次是:(1)自动触发开关、(2)开始触发、(3)立即触发、(4)停止触发。

立即触发,立即将当前 ILA RAM 中的数据上传到 Vivado,而不管触发条件是否得到满足。

移除调试代码:

将添加的代码屏蔽,将iLa文件移除工程重新进行比特流编译即可。

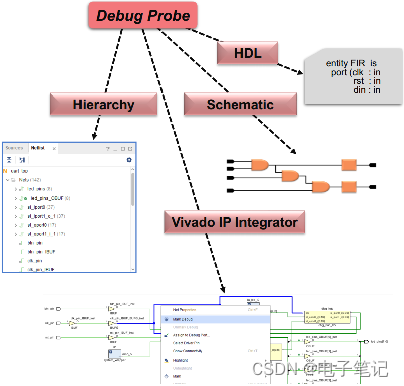

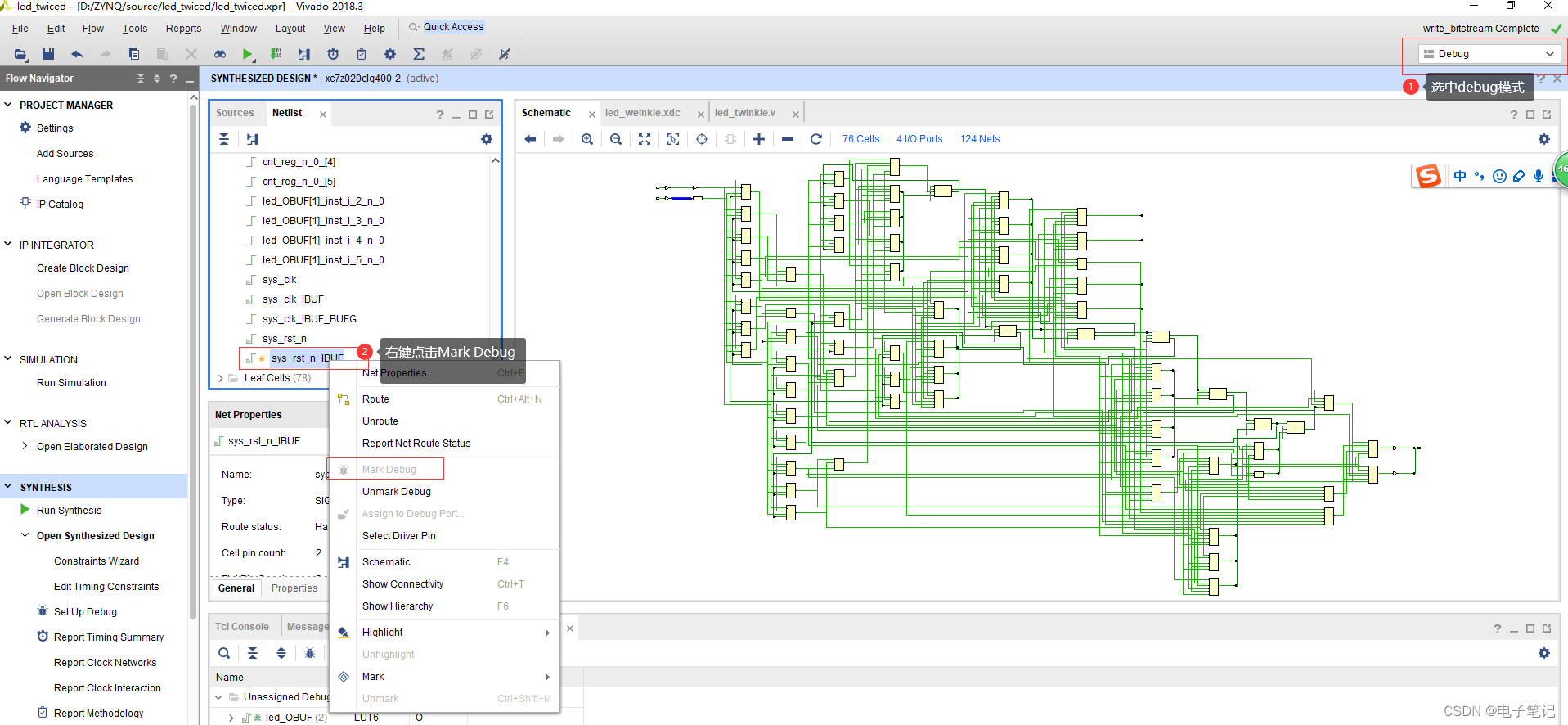

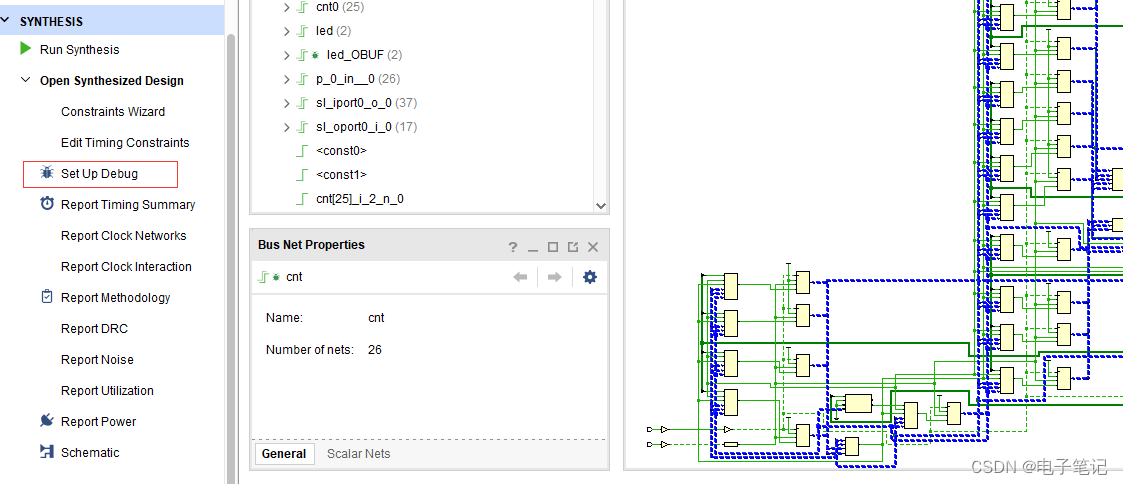

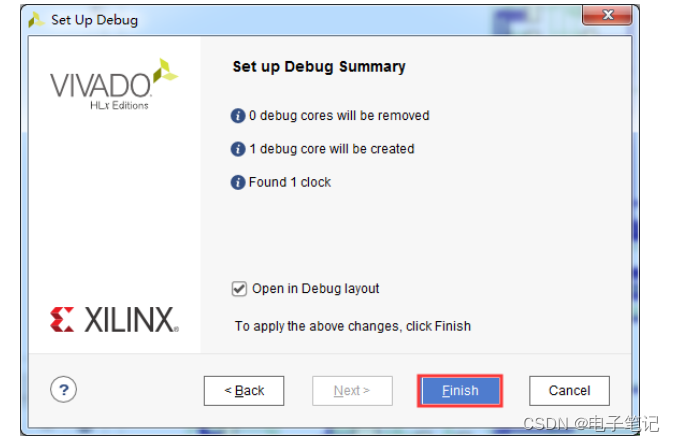

2.网表插入调试探针流程:

(mark_debug = “true”)reg [25:0] cnt ;

其中“(* mark_debug = “true” *)”必须紧挨在变量声明的前面。这样,在综合完成之后并打开综合后的设计时, cnt 信号就自动被标记了“Mark Debug”属性。此外,被添加了(*mark_debug = “true” *)属性的 reg或 wire 信号不会被工具优化掉。

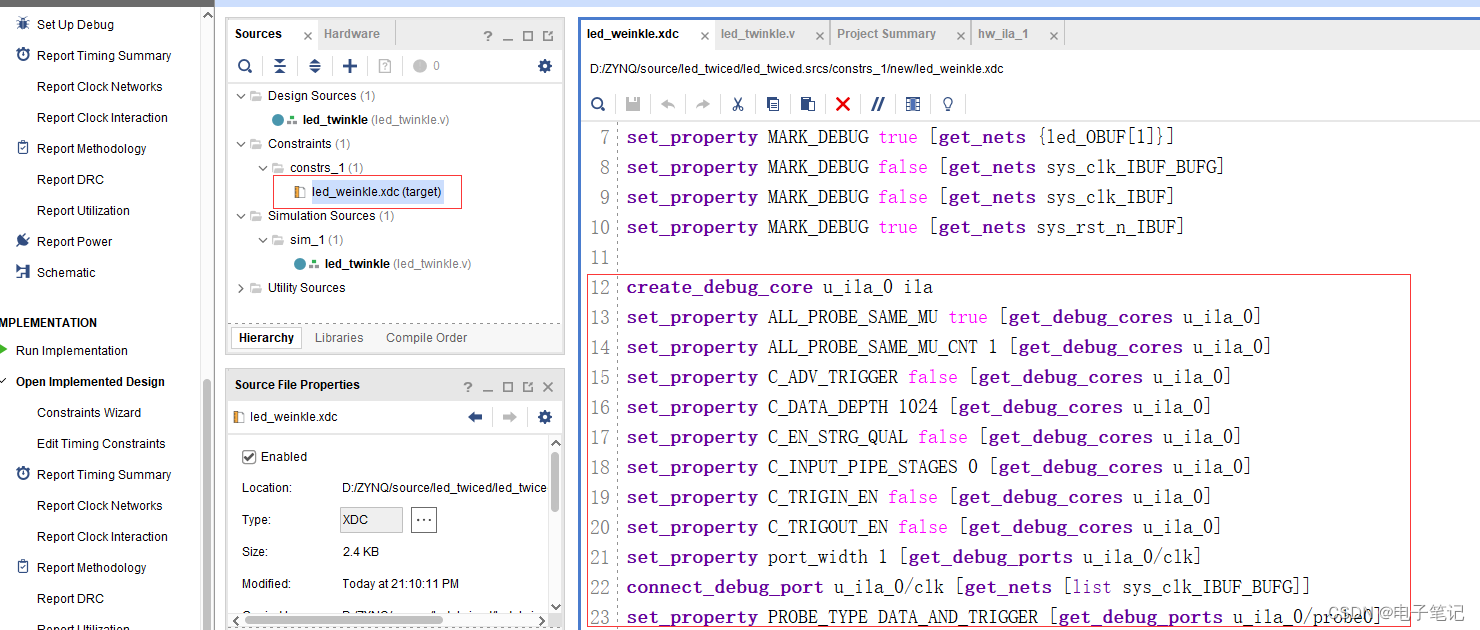

生成完成后:在XDC文件中会自动增加如下代码:

实现效果如下所示: